Protecting RISCV Against Timing Side-Channel Attacks

- Supervisor(s): Prof. Avi Mendelson

- Requirements: Computer Architecture (236267), knowledge on HDL development (optional), knowldge of hardware security (optional)

- Project document

- Status: available

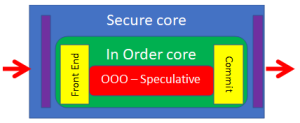

This project is based on a paper, “Secure and Speculative Core,” but this time, we would like to implement the idea as part of a RISCV architecture implemented over FPGA.

The student can choose to focus on the implementation or to extend the work (and so to make it a research project).

As part of the project, the student will extend their knowledge of how processors work, how to develop models that will run over FPGA, and more.

RISCV-based Mechanism to Recover from Security Attacks

- Supervisor(s): Prof. Avi Mendelson

- Requirements: Computer Architecture (236267), course / knowledge in security attacks

- Project document

- Status: available

Critical systems cannot be stopped if a security attack happens. An alternative is to create checkpoints and rewind the system to the last known safe-point.

This project aims to develop such a mechanism and add it to an existing RISCV implementation.

Security Counters for RISCV processor

- Supervisor(s): Prof. Avi Mendelson, Alexander Grinshpun

- Requirements: Computer Architecture (236267)

- Project document

- Status: available

SDR-based extension to RISCV processor

- Supervisor(s): Prof. Avi Mendelson, Roman Maltis

- Requirements: Computer Architecture (236267)

- Project document

- Status: available